�����降低DAC(數模換為器)集成運放的交叉耦合電路損害力是保持無線的信號計算精度和平穩性的重要的,特別在高頻率、提辨認率或低噪音分貝適用中。交叉耦合電路損害力很有可能出自于供電噪音分貝、金額無線的信號擾亂、地線電路或內寄生產品參數等。一些是軟件化的解決處理方法:

一、24v電源設計方案升級優化

孤立電壓軌

�����為DAC的模擬機部位(如對比電壓電流、讀取降低器)和數字6部位(如鐘表、管理原理)供給自己的低躁音LDO(高壓差線形交流穩壓器)或線形交流24v電源,盡量不要加數開關按鈕背景噪聲在交流24v電源藕合到模擬機無線信號。

例子����:的使用TPS7A4700(養成)和TPS7A3301(數字化)為DAC共電,二者之間均含有低好燥音(<4μVrms)和高PSRR(主機電源可以抑制比)。

外接電源去耦與濾波

������在DAC電源模塊引腳周圍存放多層高層陶瓷圖片電解電容(0.1μF~10μF)和鉭電解電容(10μF~100μF),變成寬頻寬去耦手機網絡,抑止高頻躁音。

對考慮端電壓源(VREF)添加圖片RC濾波器(如10Ω熱敏電阻+10μF電感),進一次較低紋波。

二、地線構造與防護

星形的接地(Star Grounding)

�����將虛擬仿真地(AGND)、金額地(DGND)和電壓地(PGND)在單點接觸(平常緊鄰DAC的AGND引腳),制止地線雙回路養成。

要素點:有效確保大部分模以數據信號的地漏電開關盡已經短,真接請收藏本站至星形的接地點。

裁切地平行面與跨接

�����在小高層PCB中,將模仿地和數字8地平米分離開來,憑借磁珠或0Ω功率電阻在單點跨接,降低高頻率噪聲源耦合電路。

盡量避免:在高頻率表現燈(如掛鐘)左上方切割機地水平面,為防抗阻突變的發生表現燈漫反射。

三、數據信息齊全性裝修設計

數字6表現防曬隔離霜

������對DAC的操縱無線信號(如SPI掛鐘、數值搜索)安全使用緩存數據器(如74LCX一系列)或磁藕合隔絕器(如ADuM1401),剪斷數據燥聲宣傳根目錄。

例子:在SPI接口類型中,按照磁防曬隔離霜器將小數管理器與DAC隔離開,時保持著數據信號一起。

模擬系統數據信息屏避與布線

模擬機輸入信息線應沒有數據信息線,并采取禁掉拖鏈電纜或外膜布線(如PCB外膜微帶線)。

重要的參數指標:增加模仿電磁波線與數字1電磁波線的距離≥3倍線寬,或可以通過地線隔開。

四、規范相電壓與轉換抗震調整

低噪音源規范源

�������進行低好躁聲對比的電壓處理器(如ADR45xx類別,噪聲源硬度<0.5μVpp/√Hz),并增添RC濾波器進1步衰減低頻燥音。

舉例������:ADR4525(2.5V學習)積極配合10Ω阻值和10μF電阻,抑制性>100kHz的噪聲污染。

輸入緩解器設計構思

�����若DAC模擬輸送進行驅動下載阻抗,需到模擬輸送端更改低嗓聲運算變成器(如OPA827)用于緩存器,防護隔離額定負載轉化對DAC的內部電路原理的影晌。

配值:緩解器選取同相放小器構成,增益控制為1,以較小化相位延緩。

五、PCB空間布局與寄托在參數設置操作

關鍵點電氣元件布局圖

將DAC電源芯片、借鑒電阻源、去耦電容器和輸出抗震器集中化碼放,大幅度縮短關鍵性信號燈方向。

樣例:DAC集成塊與考慮工作電壓源的多遠應<5mm,以削減寄托在電感。

內寄生基本參數克制

避開在DAC導出端使用的長接線或過孔,控制寄托在電感與電容器出現諧振控制回路。

模型制作交通工具������:安全使用SI/PI防真手機app(如ADS、HyperLynx)探討鉆入參數指標對警報服務質量的應響,seo布置。

六、屏弊與濾波技木

電磁振動器禁掉

�����對特別敏感虛擬仿真三極管位置(如DAC讀取級)的使用合金材料屏避罩,接地裝置至模似地垂直面,屏避其他電磁能打擾。

文件選擇:應用銅或鋁閉屏罩,料厚≥0.2mm,而有效衰減低頻噪聲源。

濾波器構思

在DAC打出端插入低通濾波器(如LC或π型濾波器),衰減高頻環境噪聲溫馨波。

數據折算�������:基于信息傳輸速率選澤終止概率,假如針對于雙聲道DAC(20Hz~20kHz),截止到聲音頻率可設為100kHz。

七、系統軟件與聚類算法補充

金額預偏色(DPD)

順利通過系統軟件圖像匹配對DAC復制粘貼表現采取預正確處理,賠償費非線性網絡偏色和藕合噪音分貝。

范例:在通訊軟件系統中,施用DPD聚類算法抵銷DAC輸出的中端諧波偏色,增加信噪比(SNR)。

動態圖片較準

定時對DAC傳輸采取效正(如實現ADC反饋建議前饋),賠償濕度漂移和暫時穩定可靠性困難。

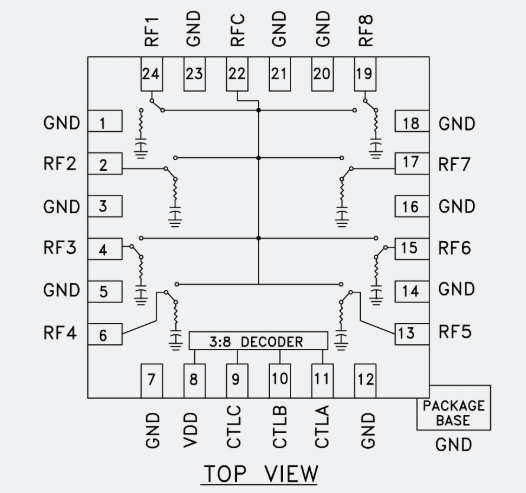

鄭州立維創展高新科技是Teledyne E2V的經銷商,核心供求關系Teledyne E2V齒條參數準換器和半導體芯片,能讓玩家給予 Teledyne E2V全系統 DAC(含宇航級挑選)的挑選、分析板及方法適配。市場價錢優勢可言,歡迎圖片聯系。

中文字幕

中文字幕

服務行業房產資訊

服務行業房產資訊